- 您现在的位置:买卖IC网 > Sheet目录1996 > HI5805BIB (Intersil)IC ADC 12-BIT 5MSPS 28-SOIC

2

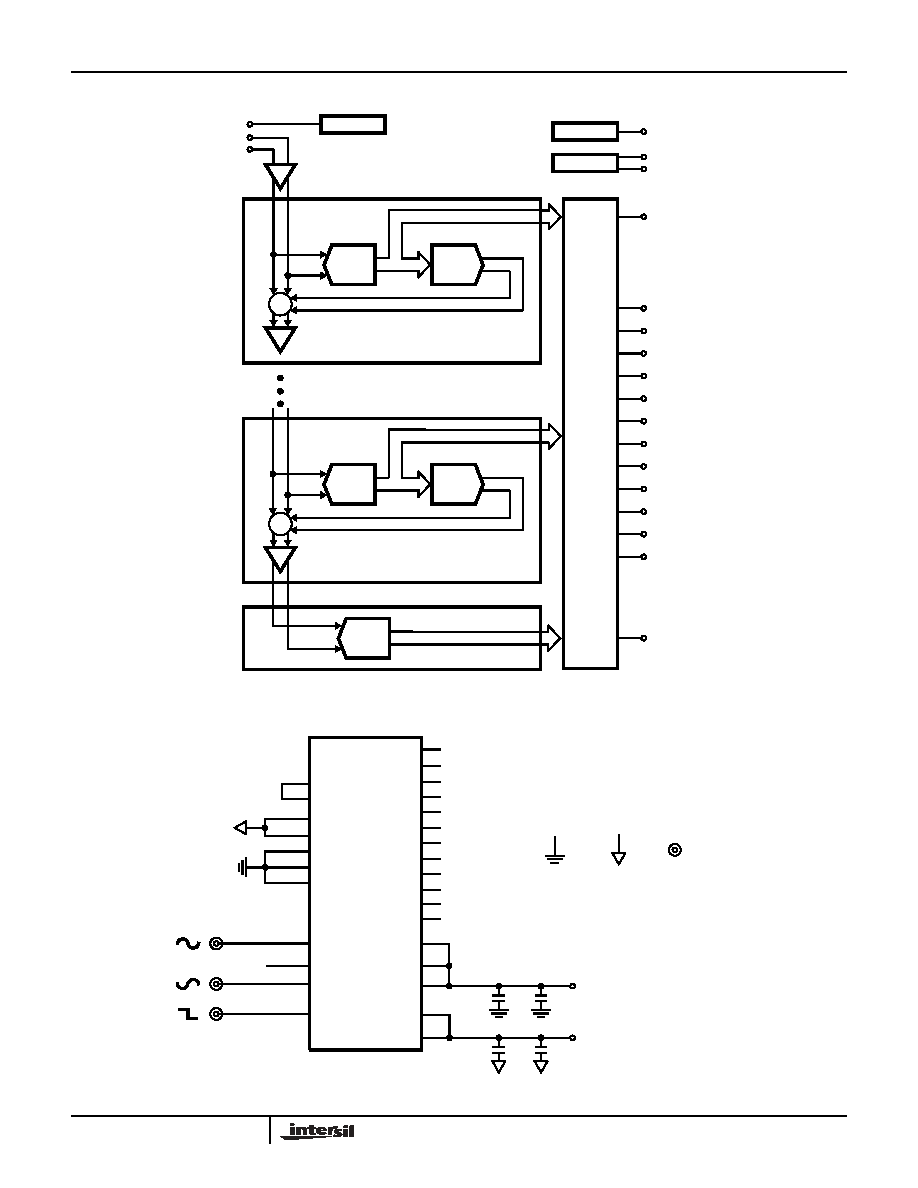

Functional Block Diagram

Typical Application Schematic

VDC

VIN+

VIN-

BIAS

4-BIT

FLASH

+

-

4-BIT

DAC

4-BIT

FLASH

STAGE 4

STAGE 3

STAGE 1

AVCC

AGND

DVCC1

DGND1

DIG

ITA

L

DELAY

D11 (MSB)

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0 (LSB)

4-BIT

FLASH

+

-

4-BIT

DAC

AND

DIGITAL

ERRO

R

CORRECTION

CLOCK

REF

DVCC2

DGND2

VROUT

CLK

VRIN

∑

X8

S/H

∑

VRIN (12)

HI5805

VROUT (11)

VIN- (9)

CLK (1)

DGND1 (5)

DGND2 (21)

DGND1 (3)

AGND (13)

(14) AVCC

(22) DVCC2

(17) D9

(18) D8

(19) D7

(20) D6

(23) D5

(24) D4

(25) D3

(26) D2

(27) D1

(LSB) (28) D0

AS CLOSE TO PART AS POSSIBLE

10

F AND 0.1F CAPS ARE PLACED

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

BNC

CLOCK

VIN+

0.1

F

10

F

0.1

F10F

+

AGND (7)

VIN+ (8)

VIN-

DGND

AGND

(2) DVCC1

(4) DVCC1

VDC (10)

(16) D10

D10

(MSB) (15) D11

D11

(6) AVCC

+5V

HI5805

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HI5812JIBZ-T

ADC 12BIT SAMPL TRK&HOLD 24-SOIC

HI5828IN

DAC DUAL 12BIT 130MHZ 48-LQFP

HI5860IBZ

CONV D/A 12-BIT 130MSPS 28-SOIC

HI5960IAZ

CONV D/A 14BIT 130MSPS 28-TSSOP

HI7188IN

CONV A/D 16BIT 8:1 MUX 44-MQFP

HI7190IP

IC ADC 24BIT PROGBL SER 20-PDIP

HI7191IP

IC ADC 24BIT PROGBL SER 20-PDIP

HI9P5701K-5

CONV A/D 6BIT 30MSPS 18-SOIC

相关代理商/技术参数

HI5805BIBZ

功能描述:模数转换器 - ADC 28 INDTEMP A/D 12BIT 5MSPS 0 5LSB V-REF RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

HI5805EVAL1

功能描述:数据转换 IC 开发工具 HI5805 EVAL PL ATFORM

RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

HI5806IB

制造商:Rochester Electronics LLC 功能描述:- Bulk

HI5808

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 9MSPS A/D Converter

HI5808_01

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 9MSPS A/D Converter

HI5808BIB

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 9MSPS A/D Converter

HI5808BIBR4499

制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:

HI5808BIBS2503

制造商:Rochester Electronics LLC 功能描述:- Bulk